# Measurement/Reference Guide For The HP 1631A/D Logic Analyzer

# Contents

| Measurement/Feature Matrix                                                                                                                                                                                                                                                                                                                                                                                                       | ••••                                  | 1                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------|

| Abstract Of Measurements                                                                                                                                                                                                                                                                                                                                                                                                         |                                       | 2<br>3                       |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       | 3                            |

| <b>Using The Digitizing Oscilloscope Within The HP 1631A/D</b><br>Introduction To Digitizing Oscilloscopes<br>Measurement 1: Getting Started With The Digitizing Oscilloscope Within The HP 1631A/<br>Measurement 2: Using The Digitizing Oscilloscope With A Trigger Condition<br>Measurement 3: Using The Markers To Determine Time Intervals And Voltage Levels<br>Measurement 4: Using Analog Post-processing To Mark Events | D                                     | 5<br>5<br>6<br>7<br>10<br>12 |

| Using The Timing Analyzer Within The HP 1631A/D<br>Introduction To Timing Analysis<br>Measurement 5: Using The Timing Analyzer To Capture And Display Some Of The More                                                                                                                                                                                                                                                           | • , • • • • • • • • •                 | <b>15</b><br>15              |

| Measurement       6: Using The Timing Analyzer And Post-processing To Determine Maximum<br>Forced Refresh Time         Measurement       7: Using Timing Post-processing To Determine Actual System Overhead                                                                                                                                                                                                                     |                                       | 17<br>21<br>24               |

| Measurement       8: Triggering On Glitches         Using The Cross-triggering Capabilities Of The HP 1631A/D          Introduction To Cross-triggering          Measurement       9: Using Cross-triggering To Find The Cause Of A Glitch                                                                                                                                                                                       | •••••••••                             | 26<br>29<br>29<br>30         |

| Using The State Analyzer In The HP 1631A/D<br>Introduction To State Analysis: The Data Domain<br>Measurement 10: Using The State Analyzer To Capture A Simple Program                                                                                                                                                                                                                                                            |                                       | 33<br>33<br>34               |

| Appendix A: Overview Of DRAMs And The DRAM Board<br>For The 5036A                                                                                                                                                                                                                                                                                                                                                                |                                       | 37<br>37                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  | · · · · · · · · · · · · · · · · · · · | 39<br>61<br>71<br>73         |

| Appendix         B: Overview         Of         FORMAT/TRACE         Menus                                                                                                                                                                                                                                                                                                                                                       |                                       | 75<br>75<br>77<br>80         |

# Measurement Feature Matrix

| Feature                                              | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10       |

|------------------------------------------------------|---|---|---|---|---|---|---|---|---|----------|

| Analog Triggering                                    | A | A | В |   |   |   |   |   |   | <u> </u> |

| Analog Markers<br>(Voltage, Time)                    |   |   | A | В |   |   |   |   |   |          |

| Analog Post-processing                               |   |   |   | A |   |   |   | 1 |   |          |

| Glitch Capture                                       |   |   |   |   |   |   |   | A | В |          |

| Timing Post-processing<br>(Cursors)                  |   |   |   |   |   | A | A |   |   |          |

| Timing Triggering                                    |   |   |   |   | A | В | В |   |   |          |

| Timing Arms Analog:<br>(Simultaneous <b>Capture)</b> |   |   |   |   |   |   |   |   | A |          |

| State Triggering                                     |   |   |   |   |   |   |   |   |   | A        |

| Mixed Display<br>(Timing Analog)                     |   |   |   |   |   |   |   |   | В |          |

| Fast Analog<br>Sample Rate                           |   | В |   |   |   |   |   |   |   |          |

A primary focus B secondary focus

# Abstract Of Measurements

**Measurement 1:** capturing and displaying the 4 MHz signals from the HP 5036A crystal with the digitizing oscilloscope. Includes an example of how to set trigger conditions for the scope.

**Measurement** 2: looking at transients on the +5V power supply line of the HP 5036A. Shows how a digitizing oscilloscope can trigger on events that it may not be able to display because of a long specified sample period.

**Measurement 3:** uses the x and o markers in the oscilloscope to measure a voltage-dependent time interval between the +5V power supply and the L = RESET IN line to the 8085.

**Measurement 4:** an introduction to using the analog post-processing capabilities to make certain the voltage-dependent time interval of measurement 3 does not violate manufacturers specifications.

**Measurement 5:** setting FORMAT and TRACE specifications and capturing six signals on the DRAM board with the timing analyzer. Includes a brief familiarization exercise on the timing analyzer.

**Measurement 6:** use of timing post-processing capabilities to measure how long the microprocessor is idle during a forced refresh. Starts with ballpark calculations from the manufacturers specification sheet then determines actual maximum time by using the post-processing time interval measurement features. Uses the results to determine how asymmetrical the DRAM refresh clock can be to improve efficiency.

**Measurement 7:** continuation of measurement 6 to determine average idle time of the microprocessor during simulated normal operation. While measurement 6 looked at only forced refreshes, this measurement includes forced and hidden refreshes. Looks at the difference in idle time between symmetrical and asymmetrical DRAM refresh clocks.

**Measurement** 8: an introduction to glitch capture with the timing analyzer. Shows how to set TRACE specifications for glitch mode and captures a recurring glitch on the DRAM board.

**Measurement 9:** continuation of measurement 8 using time-correlated analog and timing to determine cause of the glitch. Shows mixed display mode where both analog and timing channels are on the same screen.

**Measurement 10:** an introduction to the state analyzer. Captures a simple state listing and shows how to inverse assemble the listing.

## **Equipment List**

Following is a list of the equipment needed to make the measurements discussed. Each measurement lists the appropriate connections from the logic analyzer to the HP 5036A Microprocessor Lab.

- HP 1631D logic analyzer

- HP 10017A10: 1 divider probes (two each, supplied with the HP 1631D)

- HP 5036A microprocessor lab with DRAM board (DRAM board available from the HP Colorado Springs Division)

- HP 9121S/D or 9122S/D discdrive

- HP 10269B probe interface

- HP 10304B 8085 interface module with inverse assembler

- Disc 20-pin IC clips (2 each)

## Introduction

The purpose of this Measurement Reference Guide is to acquaint you with some of the features and capabilities of the 1631. It is not intended to be a complete guide to every feature, but rather to give insight into the types of measurements the 1631 can make. As much as possible, each measurement is related to the types of problems encountered by a design engineer. It does assume some level of experience in using analog oscilloscopes, but does not assume any level of expertise with a logic analyzer. With that in mind, the guide starts out in the realm of the oscilloscope and progresses into the world of logic analysis. It also addresses areas where the mating of the two yields significant advantages. Many of the measurements discussed have been previously impossible, or at best very difficult.

Should you need it, Appendix B is a brief tutorial on the format and trace specification menus that relate to each portion of of the analyzer. The tutorial describes each field in the menu for that particular portion. As each section of the guide progresses, additional menus are shown to help you set up the measurement. More information on the menus is available in the HP 1631A/D operating and programming manual (HP part # 01631-90901).

The looseleaf format of this guide was chosen to allow for expansion. It is our goal to fill the measurement/feature matrix that follows the table of contents. Although the initial printing does not do this, it will be finished after introduction of the 163 1. Notification of additional measurements for the guide will be made in the HP Instrument News letter. While many of the measurements are continuations of previous ones, the matrix should provide a reference for determining which measurements in the guide exercise which features of the 163 1.

## **Using The Digitizing Oscilloscope Within The HP** 1631A/D

### **Introduction** To Digitizing Oscilloscopes

Although most of us are familiar with the traditional analog oscilloscope, and perhaps even an analog storage oscilloscope, a digitizing storage oscilloscope offers a number of advantages. Some of these are demonstrated in the first section of this guide, but are mentioned here for sake of introduction.

One problem with an analog storage oscilloscope is its tendency to bloom or fade. Even the best of storage scopes loose their image with time, due to these factors. A digitizing oscilloscope does not suffer from this because it does not store the image on a mesh in the CRT, but rather in semiconductor memory. Because the image is stored in memory, it can be retained on-screen indefinitely without degradation. In addition, the image can be dumped from memory to a printer or mass storage device for later recall. Since the information in memory is a digital representation of the actual waveform, it can be dumped to a computer for post-processing if desired. This can be important in production environments where a waveform is tested against a standard.

When a signal has a low duty-cycle or rep-rate that requires a long sweep speed for viewing, flicker becomes a very real problem, both in terms of annoyance and representation of the signal. Again, a digitizing oscilloscope provides a stable display of the waveform without flicker. It can do this because the waveform IS kept on-screen until the next complete update is ready for display.

Often, it is helpful to view part of the waveform that occurred before the trigger point. For instance, suppose you need to look at the rising and falling edges of a sawtooth that is several milliseconds long. We suspect that the latter portion of the rising ramp is non-linear due to non-resistive loading. We can't trigger on the rising portion of the ramp and display it with an analog oscilloscope, due to its long period, so it would be very handy to trigger on the falling edge and look backward in time. The digitizing oscilloscope within the HP 1631A/D allows you to trigger on an edge and look backward in time to pre-trigger events. This capability is called negative time capture and is a fundamental feature in HP's digitizing oscilloscopes.

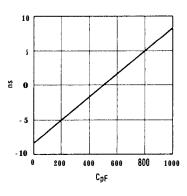

Digitizing oscilloscopes, although superior to analog oscilloscopes in many cases, make some compromises of which you should be aware. These are fundamentals in sampling theory and create inherent errors. On fast transitions, the digitizer can sample only a few points on the edge, and the hardware (or software, in the case of the HP 1631A/D) interpolator "fills in" the points in between. The digitizer must make some assumptions as to the shape, and can be optimized for either interpolator speed or accuracy of waveshape. If rise time is all-important, the interpolator can be optimized by arbitrarily changing the shape of the edge by adding preshoot and overshoot. If the accuracy of waveshape is of primary concern, rise time capture will be slower. The HP 1631A/D reaches a compromise between the two. The fidelity of the waveshape is maintained while providing a minimum rise time display of 7 nanoseconds. This means that if you could generate a zero nanosecond rise time edge, the HP 1631A/D would display it as a 7 ns rise time edge. Obviously, as the rise time becomes longer, this inherent inaccuracy becomes less of a factor.

# Using The Digitizing Oscilloscope Within The HP 1631A/D (continued)

### Measurement 1: Getting Started With The Digitizing Oscilloscope Within The HP 1631A/D.

**Problem:** using the HP 1631A/D as a real-time digital oscilloscope.

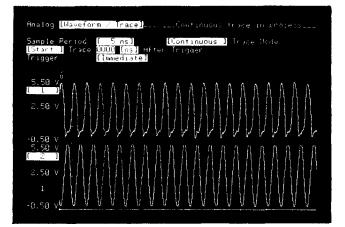

**Description:** look at the system clock in a continuous mode, with and without trigger qualification. When the HP 1631A/D is powered up, it is configured for use as a real-time scope. All that you need to do is connect the probes to the analyzer and signals and press the RUN key.

**Setup:** connect two HP 10017A probes to the channel 1 and channel 2 BNCs on the front panel beneath the keyboard. Connect channel 1 to pin 1 of the 8085 microprocessor in the HP 5036A microprocessor lab and channel 2 to pin 2 of the processor. Power up the HP 1631A/D and press the RUN key. You should have a 4 MHz signal on both channels 180 degrees out of phase with one another.

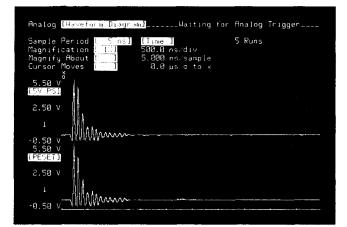

#### Figure 1

Notice that the message across the top of the screen tells you that you are in the analog portion of the analyzer and that you are using the [Waveform/Trace] display. This is the real-time oscilloscope display. Also notice that the analyzer is in the continuous mode. Let's set a trigger condition for the oscilloscope. Using the CURSOR keys, move the cursor down to the field labeled [Immediate].\* This is the trigger condition. [Immediate] means that the analyzer starts to store data as soon as the RUN key is pressed and that it has no qualification. Press the NEXT[] key. The trigger condition is now set for channel 1 and a rising edge with a trigger threshold of O.OOV. Move the cursor to the [Rising] field and press the NEXT[] key. The trigger edge is now [Falling]. Use the cursor keys to move to the trigger level field and enter a new threshold of 1.4 V from the HP 1631A/D's keyboard. The oscilloscope is now triggering on a falling edge of channel 1 at a threshold of 1.4 V. The trigger channel can be changed to channel 2 or to the external trigger channel.

One last condition of importance in this menu is the sample period. It can be changed from 5 ns to 500 ms in a 1-2-5 sequence.

**Conclusion:** congratulations! You have just made your first measurement with the HP 1631A/D. Although not too complicated, it demonstrates how easy it is to use the analog portion of the HP 1631A/D **as** a real-time digital oscilloscope. The following measurements and sections, we will investigate further the power of the 1631.

\*There will be same delay between when you press the cursor key and when the cursor moves when the analyzer is running. This is normal, as the HP 1631A/D acts on keyboard presses only between acquisitions.

### Measurement 2: Using The Digitizing Oscilloscope With A Trigger Condition.

**Problem:** trigger on and display power supply noise on the microprocessor +5 V supply line and the RESET line.

**Description:** the microprocessor has a RESET line that is used to initialize it on power-up. When the RESET line reaches threshold (2.4V), the processor starts normal operation. However, the line cannot just be connected to the 5 V power supply, because the microprocessor needs 10 ms between when the supply line reaches 4.75 V and when the RESET line crosses through the threshold. This allows time for an internal oscillator to stabilize. To make certain that the RESET line waits for at least 10 ms to cross threshold, an RC network is installed to integrate the power-on pulse.

When the system is powered up, several voltage excursions appear on the line. With an analog storage oscilloscope, these would be difficult to see and still keep the sweep speed low enough to see the slow RESET transition. We will look at these transitions with the 1631 to illustrate a basic advantage of a digitizing oscilloscope the ability to capture and display low rep-rate signals stably.

**Setup:** power up the HP 1631A/D. On-screen is the System Configuration menu which shows the current configuration of the analyzer. At power up, the HP 1631A/D is configured for use with only two analog channels. This is the configuration we will use for the next three measurements.

Connect two HP 10017A probes to the channel 1 and channel 2 BNCs on the front panel beneath the keyboard. Connect channel 1 to pin 40 of the 8085 in the HP 5036A microprocessor lab. This is the +5 V supply line. Connect channel 2 to pin 36 of the 8085, which is the L = RESET IN line.

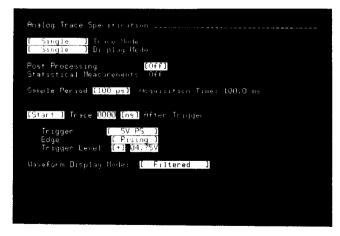

Press the FORMAT key, which is one of six along the top of the HP 1631A/D keyboard. This brings up the format configuration menu to allow you to set the format for the measurement. Change it to match figure 2.

###

#### Figure 2

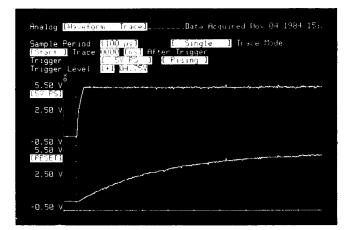

Press the TRACE key, which is one of six along the top of the HP 1631A/D keyboard. This brings up the trace configuration menu to allow you to set the trace conditions for the measurement. Change it to match figure 3.

| Analog Trace Specification                                                   |

|------------------------------------------------------------------------------|

| ( Single ) Trace Mode<br>[ Single ] Display Mode                             |

| Post Processing [[[[]]]<br>Statistical Measurements Off                      |

| Sample Period [100 jps] Acquisition Time: 100.0 ms                           |

| (Start ) Trace 1000 [ns] After Trigger                                       |

| Trigger ( <u>SV PS)</u><br>Edge ( <u>Pising</u> )<br>Trigger Level (+) 04.55 |

| Waveform Display Mode: [ Filtered ]                                          |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

#### Figure 3

Power the 5063A off. Press the RUN key on the HP 1631 and power up the HP 5036A. Be sure to wait 4 or 5 seconds between when power to the HP 5036A is turned off and then turned on again to allow the power supply filter capacitors to discharge. A display similar to figure 4 should be on-screen.

Note: the +5 V power supply in some HP 5036As may not reach 4.75 volts. If you have one, change the trigger voltage for channel l of the 1631 to 4.5 volts. This is not the voltage specified by the manufacturer, but will still Serve to illustrate the point.

# Using The Digitizing Oscilloscope Within The HP 1631A/D (continued)

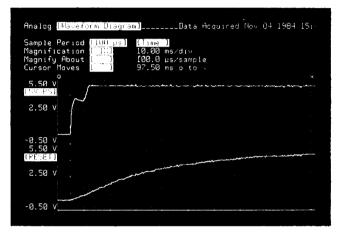

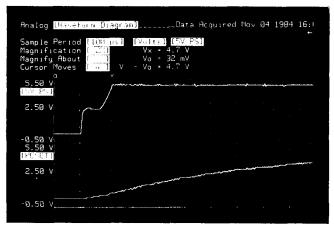

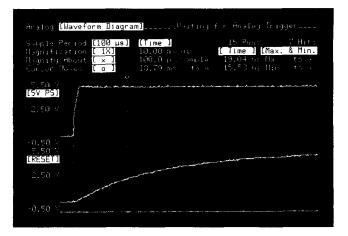

#### Figure 4

The tracepoint is shown at the left portion of the screen as a vertical dashed line. Notice that, at first inspection, the trace point doesn't appear as though it is at the 4.75 V trigger level we set for channel 1. Let's magnify the trace to see. Make sure the cursor is in the [Waveform/Trace] field, and press the NEXT[] or PREV[] key. This brings up the analog waveform diagram to allow more detailed analysis.

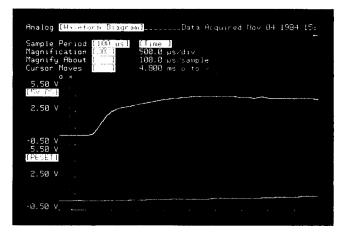

Figure 5

Using the CURSOR keys, move the cursor to the Cursor Moves field. This specifies which marker (x or o) can be moved along the waveform by the CURSOR keys. Again using the CURSOR keys, move the x marker to the tracepoint on the waveform, so we can magnify around the trace point. The HP 1631A/D always magnifies around one of the markers, as indicated by the Magnify About field. Move the cursor to the Magnification field and select [20X] with the NEXT[] key. Looking at the waveform, our previous suspicions seem to be confirmed. The trace point isn't on the rising edge of the power supply, let alone 4.75 V! Is the analyzer broken?

Obviously, it isn't, or we wouldn't have led you down this path. Instead, we are showing you a real advantage of a digitizing oscilloscope-the ability to trigger on events, even when it cannot display them due to a long sample period.

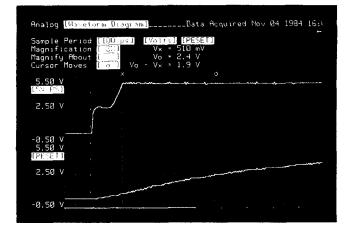

Change the magnification back to [1 X] and the sample period to 1  $\mu$ s. Press the RUN key on the 1631 and cycle the power switch of the HP 5036A and capture another trace (be sure to wait two or three seconds between cycles to allow the power supply filter caps to discharge). You should have a display similar to that shown in figure 6.

| Analog [Way                                              | eform Diagram | ]                  | _Waiting | for | Analog          | Trigger |

|----------------------------------------------------------|---------------|--------------------|----------|-----|-----------------|---------|

| Sample Peri<br>Magnificati<br>Magnify Abo<br>Cursor Move | ut ( )        | 100.0 μ<br>1.000 μ |          |     | 2 Runs          |         |

| 5.50 V<br>[5V P5]                                        |               |                    |          |     |                 |         |

| 2.58 V                                                   |               |                    |          |     |                 |         |

|                                                          |               |                    |          |     |                 |         |

| -0.50 V<br>5.50 V<br>(PESET1                             |               |                    |          |     |                 |         |

| 2.50 V                                                   |               |                    |          |     |                 |         |

|                                                          |               |                    |          |     |                 |         |

| -8.50 V                                                  |               |                    |          |     | ····· ··· ····· | ······  |

At the tracepoint, you see an excursion that the analyzer indicates is the first positive crossing of 4.75 V. Even at this sample rate, the analyzer may not display a spike that appears to go to 4.75 V. We chose this sample rate to show the beginning of the rising edge of the actual power up ramp.

For curiosity's sake, let's decrease the sample period to the minimum of 5 ns. Press the RUN key on the 1631 and cycle the power switch on the HP 5036A until the oscilloscope triggers. At this rate, you can readily see what the oscilloscope is triggering on, and we can also see that the excursions do cross our trigger level of 4.75 V.

#### Figure 7

**Conclusion:** although the oscilloscope could not display the ringing before the supply ramped up, it told you that they were there by means of the tracepoint. By decreasing the sample period, we could capture and view the voltage spikes that were triggering the oscilloscope. It would be impossible to capture the same transitions with an analog storage oscilloscope and achieve this kind of viewing resolution. In the HP 1631A/D, this resolution is made possible by a 200 megasample-per-second rate.

# Using The Digitizing Oscilloscope Within The HP 1631A/D (continued)

## Measurement 3: Using The Markers To Determine Time Intervals And Voltage Levels.

**Problem:** Measure from the time the +5 V power supply of the 5036A Microprocessor Lab reaches 4.75 V until the RESET line reaches 2.4 V (threshold).

**Description:** From the description given in measurement 2, remember that the period from when the +5 V supply voltage reaches 4.75 V until RESET crosses threshold must be at least 10 ms to ensure that an internal oscillator has stabilized. If the time is less than 10 ms, the manufacturer does not guarantee proper operation of the processor. An RC network consisting of a 3.3  $\mu$ F capacitor and a 10k  $\Omega$  resistor is attached to integrate the power up ramp applied to the RESET line. This should yield an RC time of 33 ms. But what is the actual time interval between the points in question? In this measurement we will use the markers on the waveform to find out.

Set up: To make the measurement we use the same trace specification as in measurement 2 with the exception of using single trace mode. Again we set the trace point to channel 1 (+5 V power supply) and 4.75 V on the rising edge. Even though we know the scope will trigger before the actual power supply ramp, you'll see that it will provide a good starting point.

Connect channel 1 to pin 40 of the 8085 and channel 2 to pin 36.

#### Figure 8

Turn the pow-er to the 5036A off, and press the RUN key on the 1631 Turn the 5036A power on, and note the waveform. It should look similar to the one we captured in measurement 2.

Note: rhe +5 V power supply in some HP 5036As may nor reach 4. 75 volts. If you have one, change the trigger voltage for channel 1 of rhe 1631 to 4.5 volts. This is not rhe voltage specified by the manufacturer, but will still serve to illustrate the point.

#### Figure 9

If your 1631 shows the [Waveform/Trace] display, move the cursor to the [Waveform/Trace] field and use the NEXT[] key to select the [Waveform Diagram] display. As you may recall from the previous measurement, this display allows us to use the markers on the waveform and to expand the display. Move the x marker to the trace point (the bright vertical dashed line at the left of the display). Change the Magnify About field to [x] and select Magnification [2X]. If the trace point is too far to the left of the screen, you can use the SHIFT and ROLL keys to move the waveform closer to the center of the screen. Now that the waveform is expanded, it will be easier to see where to move the x and o markers.

#### Figure 10

Move the cursor to the [Time] field and change it to [Volts]. This field specifies what the markers will read time intervals or voltages. Since we want to find the time interval between two channels, we will start with the x marker on the power supply ramp at the 4.75 volt point. As the x marker is moved, notice that the voltage is displayed on screen. The field to the right of the volt/time field is used to select the channel the markers are reading.

#### Figure 11

Keposition the cursor to this field and change the channel to RESET with the NEXT[] or PREV[] key. Change the Cursor Moves field to [o] and move the o marker to the 2.4 volt level on channel 2, as shown in figure 12.

#### Figure 12

Change the marker function back to [Time] and read the time displayed from the x to o marker. Making a time interval measurement based on voltage is that easy! We can see in figure 13 that the time margin is well within the specifications given by the manufacturer.

**Conclusion:** Use of the markers in the digital oscilloscope make time interval and voltage measurements an easy task. This is especially important when a time interval is critical in a design.

# Using The Digitizing Oscilloscope Within The HP 1631A/D (continued)

## Measurement 4: Using Analog Post-processing To Mark Events.

**Problem:** Measure from the time the +5 V power supply of the 5036A Microprocessor Lab reaches 4.75 V until the RESET line reaches 2.4 V (threshold) in a continuous trace mode. If the time is less than the 10 ms the manufacturer requires, stop the analyzer. Otherwise, develop statistics on the time interval and display the maximum and minimum.

**Description:** The two previous measurements have concentrated on measuring the time interval from when the +5 V power supply reaches 4.75 volts at power up to when the RESET line reaches 2.4 volts. Since the manufacturer specifies that the time must be at least 10 ms, we want to check the RC integrator on the RESET line to make certain that the time constraint is not violated. If the time is ever less than 10 ms, we want the scope to stop and capture the violation. But even if the time is not less than 10 ms, we would like to gather some statistical information about the time interval, specifically the minimum time.

In this measurement, we will use another powerful feature of the digitizing oscilloscope in the 1631—post processing. The post processing feature has two parts, post acquisition triggering and statistical measurements.

Post-acquisition triggering is a sort of triggering after the fact. When we set trigger and trace specifications for the scope, we are qualifying data to store in memory. This data is then displayed on screen. Post processing allows us to tell the 1631 to check for specific events in the acquired data. If these events occur, the 1631 will record a "hit", and stop if it is in single trace mode, or make another acquisition if in continuous. If in continuous trace mode, the number of runs (acquisitions) is displayed on screen as well as the number of hits (post acquisition events).

The 1631 is also capable of displaying statistical information about the hits in memory, like the maximum and minimum time between events or the mean time and standard deviation of the events.

Last, but certainly not least, we can cause the 1631 to search the acquired data for an event and stop if it finds one. This is an important capability because in certain cases it may be necessary to look at the data that led to that event. By stopping the analyzer when the event occurs, we have captured data leading up to it. You can use this capability as a sort of baby sitter to capture the desired event. We use essentially the same trace specification as in the previous measurement, with two basic changes. First, we will change the trace mode back to [Continuous]. Second, we will turn the Post Processing and Statistical Measurements fields to [On]. When the Post Processing field is changed to [On], notice that a bracketed field appears at the top of the trace specification menu, labelled [Trace Specification]. This field allows you to select the analog trace specification menu (that we have used in the last two measurements) or a post processing trace menu.

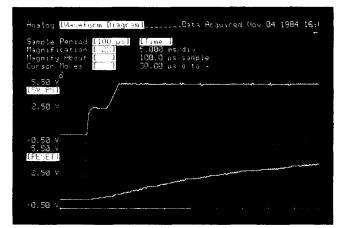

**Set up:** Connect channel 1 probe to pin 40 of the 8085 and channel 2 to pin 36. Press the TRACE key and set the trace specification as shown.

| Analog (Disce Specification)Waiting for Analog Trigger                                      |  |

|---------------------------------------------------------------------------------------------|--|

| (Lontrouvus   Trace Mode<br>  Single   Display Mode                                         |  |

| Post Processing (Un)<br>Statistical Measurements (Un)                                       |  |

| Sample Period [100 ped] Acquisition Time: 100.0 ms                                          |  |

| (Start ] Trace 0000 [ms] After Trigger                                                      |  |

| Trigger ( <u>5V PS</u> )<br>Edge ( <u>1 Pising</u> )<br>Trigger Level (1) <del>04,5</del> 8 |  |

| Waveform Display Mode: [ Filtered ]                                                         |  |

|                                                                                             |  |

|                                                                                             |  |

#### Figure 14

After the trace specification is set as shown, press the TRACE key again (this moves the cursor to the top field in the menu; neat, huh?). Press the NEXT[] or PREV[] key, which puts you into the post processing trace specification menu. Change the post processing menu to match the one shown.

#### Figure 15

What does this all mean? We have just told the 1631 to look through the data it will capture and place the x and o markers as shown. In other words, after every acquisition the 1631 will check for the first rising after the trace point which goes through 4.75 volts on the +5 V power supply (channel ]). It' it finds one, the x marker will be placed on that point. It will then look for the first occurrence of a rising edge going through 2.4 volts on the RESET line (channel 2). If it finds one, it will place the o marker on that point. If both of these events occur in one acquisition, a hit is recorded and the analyzer starts the next acquisition, If they do not occur, or if only one occurs, the analyzer does not record a hit and it starts the next acquisition. Notice the field at the bottom of the menu. This tells the 1631 to stop its continuous trace mode if the time between event x and event o is less than 10 ms. When set, the analyzer will stop should it ever encounter an acquisition when the time between the 4.75 volt point of the +5 V power supply, and the 2.4 volt of the RESET line is less that 10 ms. It could also be set to stop should the time exceed 10 ms, but that would make no sense for this measurement. If the 5036A was designed properly, this event (10 ms) will never occur.

Note: us with measurements 2 and 3, you may encounter a 5036A + 5 V power supply that does not reach 4.75 volts. If this is rhe case, change the trigger and post-processing level for channel I to 4.5 volts. Even though this is nor the voltage specified by the manufacturer, it will still serve to illustrate our point.

Press the RUN key on the 1631 and cycle the power switch on the 5036A a number of times. The 1631 will probably trace on the power up and power down portions of the cycle, since at power down there well may be transients that meet the trace specification. You should also notice that the 1631 shows the number of runs and hits in the upper right of the display. Remember that "runs" is the number of times that the trace specification is met (in other words, the number of acquisitions) and "hits" is the number of times the post processing specification is met.

#### Figure 16

The field below the number of runs should display [Time]. When in the time display, the field to the right of it (under the number of hits) is used to select the statistical information. You can select [Max. & Min.] or [Mean & Dev.]. The max and min display tells the minimum and maximum times encountered between the specified post processing events. Change the field back to [Max. & Min.].

Change the [Time] field discussed above to [5V PSx]. The screen now displays the maximum and minimum values encountered for channel 1 (5V PS) at the x marker. Since this was specified in the post processing menu, the maximum and minimum values should be the same. You can use this field to get information about both markers on both waveforms. Cycle through them and observe the ranges possible.

**Conclusion:** Post processing of the analog channels in the 1631 allow you to gather time interval statistics for verification of design criteria, as well serve as a babysitter for critical events. If such an event should occur, the analyzer can be instructed to stop, while having captured the data that led to it.

## Using The Timing Analyzer Within The HP 1631A/D

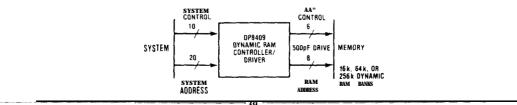

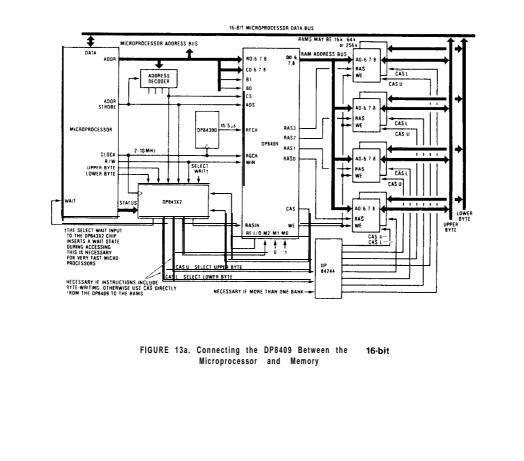

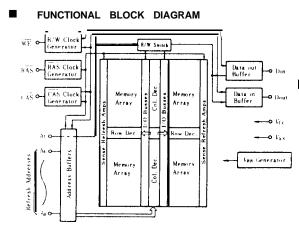

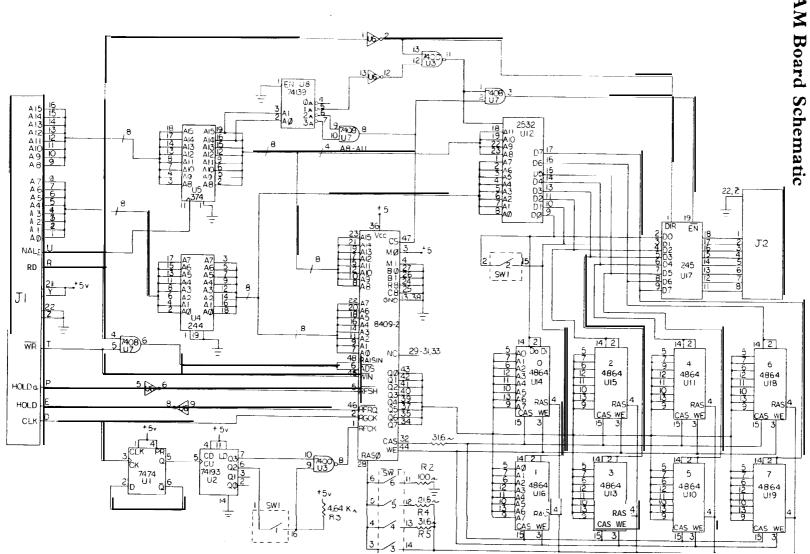

In this section of the guide, we will use a new target system as part of the HP 5036A microprocessor lab. It is an extension memory board that plugs directly onto the edge connectors of the HP 5036A and provides an additional 64k of memory. Even more important than the memory size, however, is the type of memory used. Dynamic RAM (DRAM) was chosen for a number of reasons. First, DRAMs are bring designed into an ever increasing number of new projects. Second, because of timing and other constraints, they present some unusual and sometimes frustrating problems not often encountered in static memory designs. A number of these problems are addressed directly by the feature set of the HP 1631A/D, as you will see in subsequent measurements. Third, even though the HP 5036A is not a state-of-the art microprocessor design, the concepts used to address the DRAMs here are a subset of those used in all microprocessor systems that incorporate DRAM.

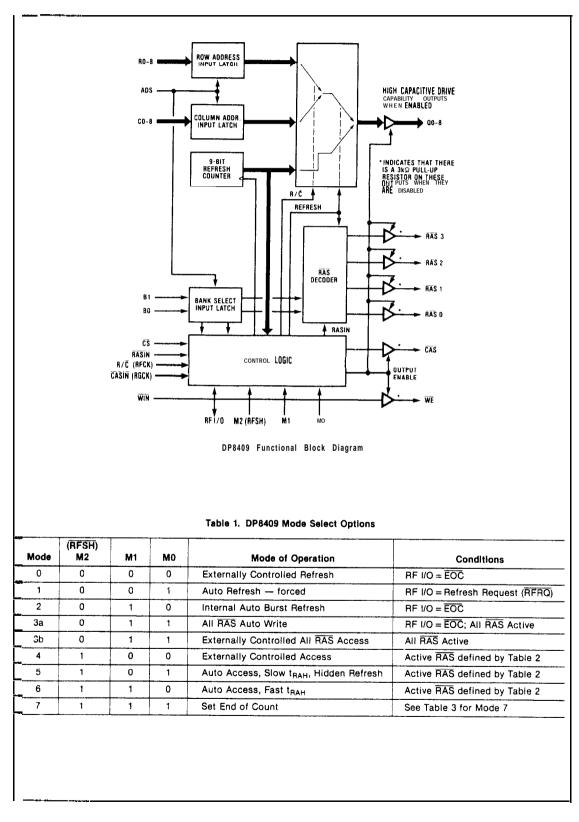

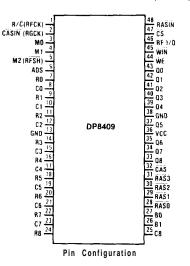

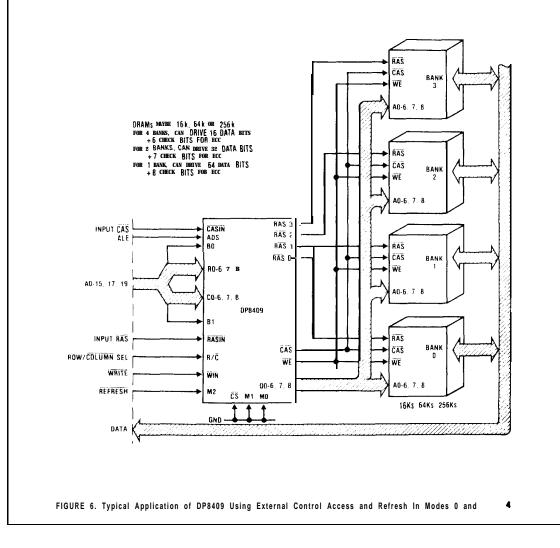

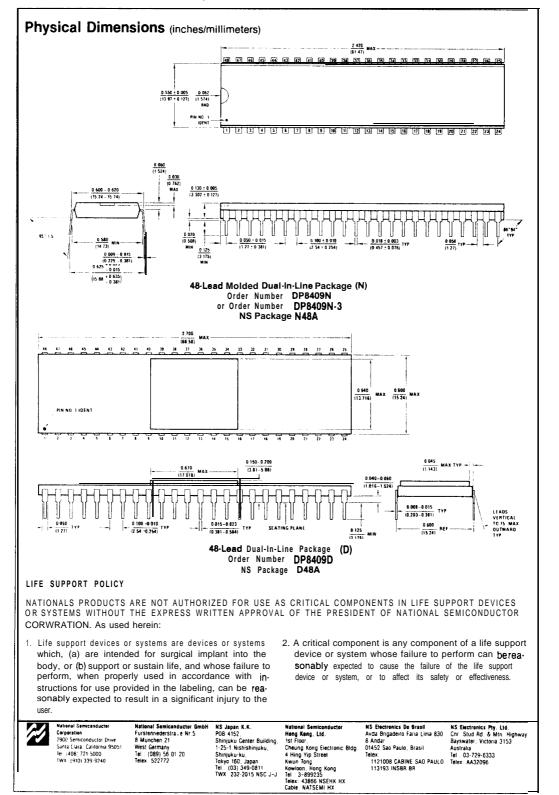

The challenge in designing with DRAMs is to make them appear as static RAM to the microprocessor. This is often easier said than done. A DRAM controller chip on the board (i.e., a National 8409) makes the task much easier and more predictable. It accepts a few signals from the processor and generates the necessary control and clock signals for the DRAMs.

Before plugging the DRAM board onto the edge connectors of the 5036A, you will need to cut trace J l near the 8085 processor. This enables the DRAM board to exercise the HOLD line when needed. Once this trace is cut, it will be necessary to reinsert a jumper into J1 if the 5036A is to be used without the DRAM board. If the jumper is not inserted, and the DRAM board is not connected, the 5036A may not work.

If you have not had exposure to memory systems in general and DRAM systems in particular, we suggest you go through Appendix A and get some exposure to the theory behind the DRAM board. This will make the timing analysis section much more meaningful.

## Introduction to Timing Analysis

Before we delve into the second portion of the HP 1631A/D, a brief discussion of what a timing analyzer is would be in order.

First, what is a timing analyzer? As digital circuits and microprocessors developed in complexity through the late 1960s, and early 1970s, it became ohvious that oscilloscopes had a number of shortcomings for testing these circuits. First, there were usually eight to 16 lines that were of interest in a bus 'structure from a microprocessor, and the designer needed to know what was occurring on all at the same time. Oscilloscopes simply did not have enough channels. Second, the designer often wasn't as concerned about the actual waveshape as when the signal crossed the logic threshold to become a 1 or 0. It was also necessary to know the relationship of these signals in to time. Thus, there was a need to trigger on a particular pattern of levels on all of the lines (we refer to this pattern triggering or pattern recognition). In some cases a list representation of the waveforms with 1s and 0s was also extremely helpful. An oscilloscope could trigger on one input, but not a combination of many inputs at the same time, and it certainly couldn't generate a list of Is and 0s. Last, it was sometimes necessary to look at the patterns on the chosen lines before the trigger pattern, perhaps to determine what may have caused an error in xubsequent patterns.

# Using The Timing Analyzer Within The HP 1631A/D (continued)

Out of these needs came the timing analyzer. Like the oscilloscope, the X-axis was time and the Y-axis, voltage. Unlike the oscilloscope, however, the data was sampled asyncronously and had a number of channels for checking a bus structure. To the timing analyzer, only one voltage is of concern-the threshold. Everything above the threshold is a high or 1, while everything below is a low or 0 (assuming positive logic). It is important to remember that the timing analyzer is not intended to make parametric measurements; that is the realm of the oscilloscope. By the same reasoning, the oscilloscope is not an effective tool in the realm of timing analysis. Each has its own strengths.

The timing analyzer in the HP 1631A/D allows you to trigger on not only levels, but on edges or a combination of the two. It can trigger on glitches; a glitch is any signal that crosses the logic threshold twice between sample periods of the analyzer. A valid pattern duration can be set that specifies a period of time for which the set pattern must be true in order for the analyzer to recognize it as valid. Timing can be shown in a list, which often makes it easier to follow complex patterns.

We will explore these capabilities in this section, and attempt to take some of the mystique out of timing analysis. Since it is in the same domain-time-as the oscilloscope, it is really a fairly easy tool to learn to use effectively.

### Measurement 5: Using The Timing Analyzer To Capture And Display Some Of The More Important Signals On The DRAM Board.

**Description:** as was mentioned in the introduction to this section, a timing analyzer has many advantages over an oscilloscope when looking at a number of digital signals with the need to trigger on a particular pattern. In this case, parametric information is not needed, as we are concerned only with the timing of the signals.

Set up: connect the lines of pod 0 (timing pod) to the points listed below on the DRAM board. Use the grabbers provided with the HP 1631D clip onto the points listed below.

| Pod 0 Bit | DRAM Board Connection | Point Signal Name |

|-----------|-----------------------|-------------------|

| 0         | U9 8409 pin 1         | RFCK              |

| 1         | U9 8409 pin 28        | RAS               |

| 2         | U9 8409 pin 32        | CAS               |

| 3         | U9 8409 pin 46        | RFREQ             |

| 4         | U9 8409 pin 5         | RFRSH             |

| 5         | U9 8409 pin 2         | RGCK              |

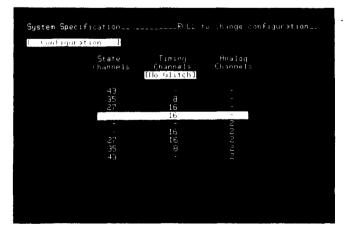

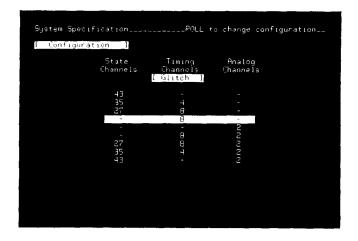

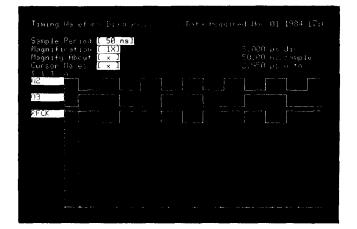

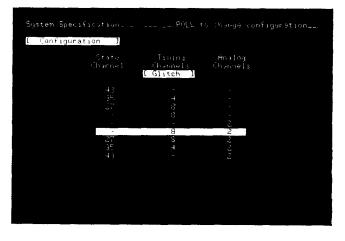

Since you will be using the timing analyzer, you must set the system configuration as shown in figure 17. The system configuration menu is reached by pressing the SYSTEM key, which is one of the six along the top of the keyboard. Change the configuration using the ROLL keys.

#### Figure 17

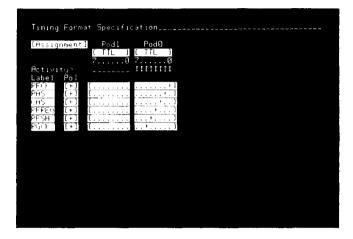

Press the FORMAT key and configure the format menu to match the one shown in figure 18.

#### Figure 18

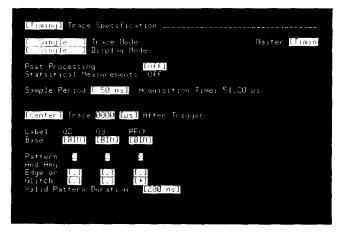

Everything is now set except the tracepoint. Press the TRACE key and set the trace as shown in the example trace menu figure 19.

| Timing Trace Specification                                                            |

|---------------------------------------------------------------------------------------|

| ( <u>Single</u> ) Trace Mode<br>( <u>Single</u> ) Display Mode                        |

| Post Processing [[14]]<br>Statistical Measurements Off                                |

| Sample Period [ 20 ns] Acquisition Time: 20.48 µs                                     |

| [Start ] Trace 0000 [ps] After Trigger                                                |

| Label) RFCK RAS CAS RFREQ RFSH RGC)<br>Base > [[BTH1] [[BTH1] [[USP]] [[USP]] [[BTH1] |

| Pattern 📓 📑 🖬 (1997-1993) 🗿                                                           |

| And Any<br>Edge [1] [.] [.] [.]                                                       |

| Valid Pattern Duration > [200 ns]                                                     |

|                                                                                       |

|                                                                                       |

Figure 19

# **'Using The Timing Analyzer Within The HP 1631A/D** (continued)

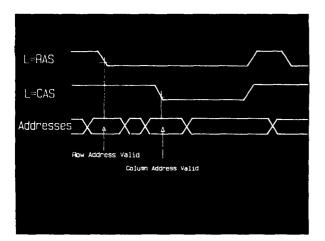

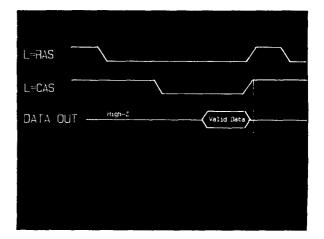

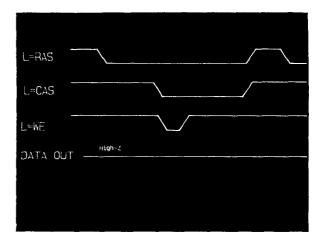

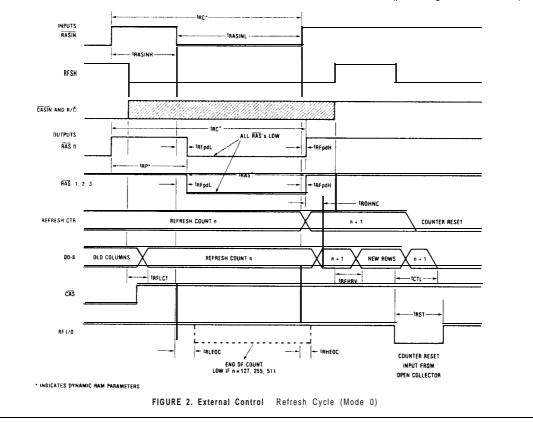

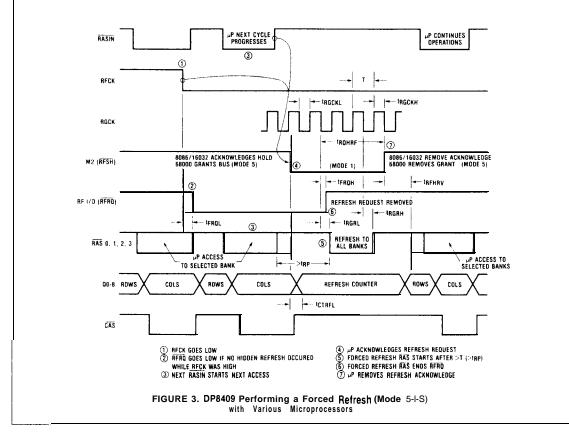

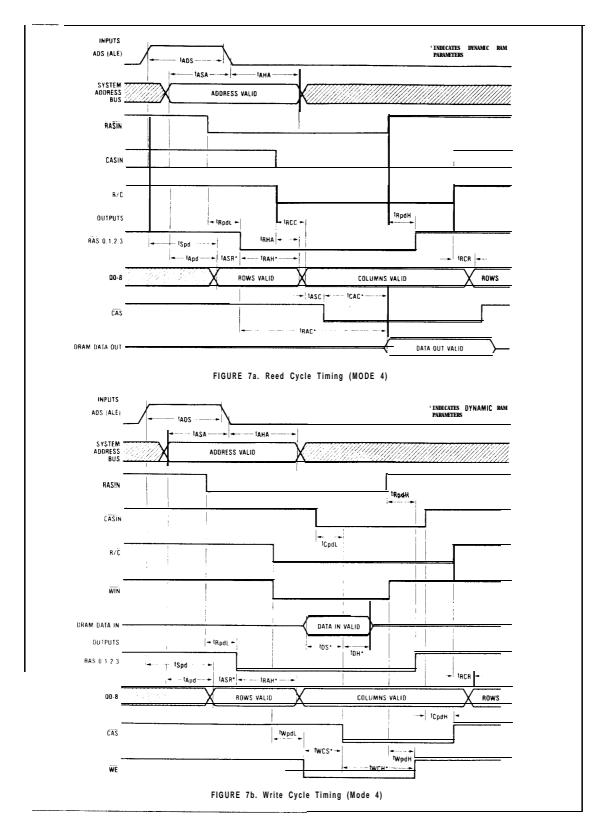

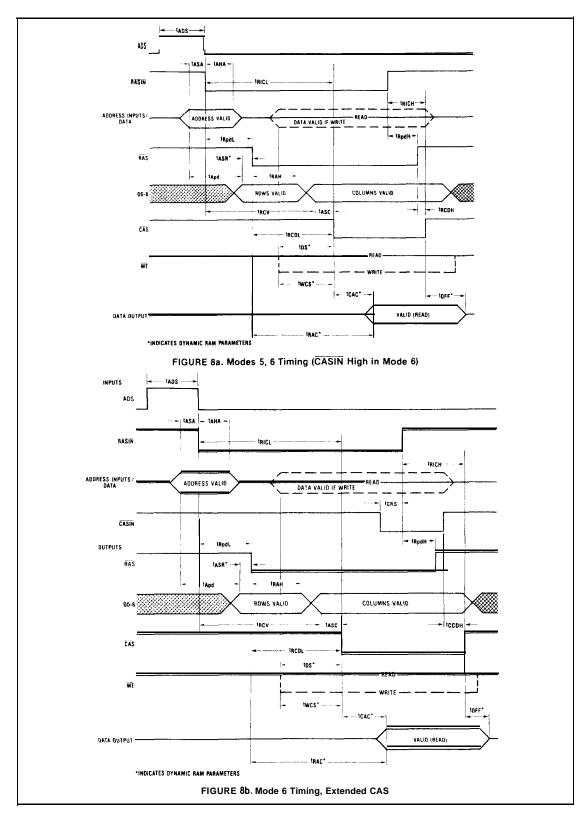

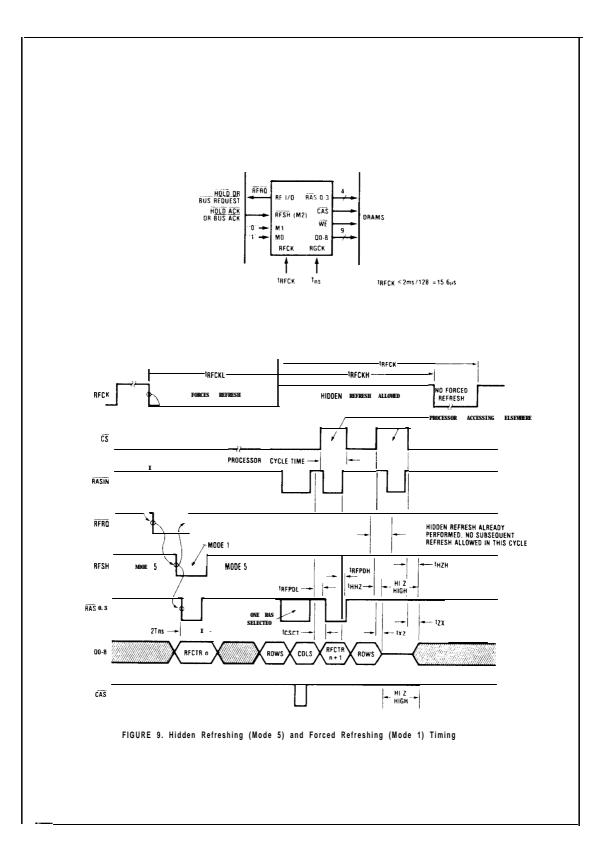

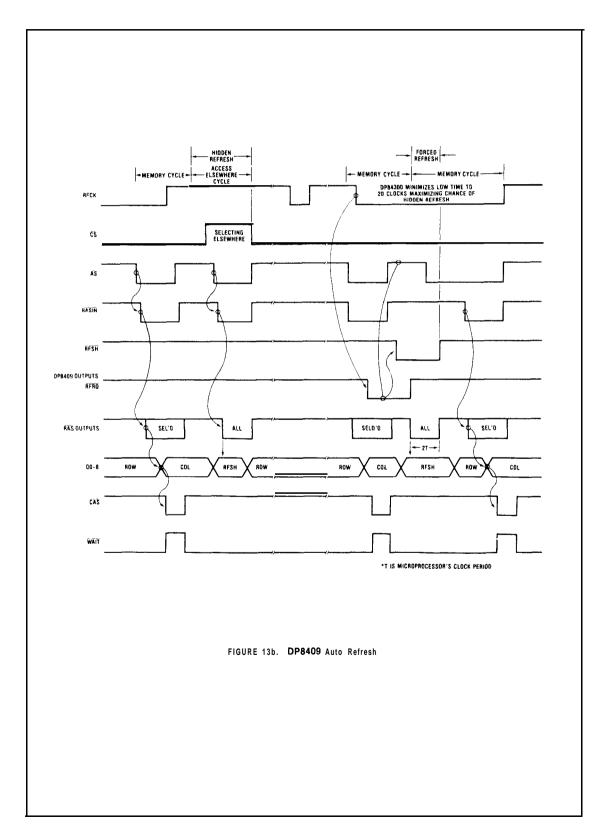

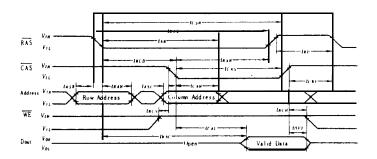

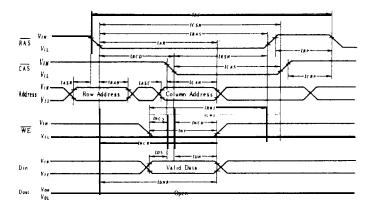

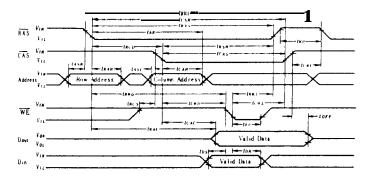

The tracepoint tells the analyzer to look for an occurrence of a negative transition of RFCK and don't cares on all of the other lines. This allows us to capture the second portion of the refresh cycle for the DRAMs. Recall from the overview in Appendix A that in our DRAM system, if a hidden refresh has not occurred during the rime that RFCK is high, the 8409 DRAM Controller requests that the microprocessor suspend operation (HOLD) while it refreshes the current row in all of its DRAMs. If a hidden refresh has occurred, the 8409 does not issue a HOLD request. In the case that a hidden refresh has not occurred, our trace should show RFCK going low and RFREQ (pin 5) going low a maximum of 30 ns later. Some time after that, the HOLD should be acknowledged by the microprocessor through pin 46 (RFSH) of the 8409 and. it will proceed with the forced refresh.

In the case that a hidden refresh has occurred while RFSH was high, a flag 15 set internally in the 8409 to tell it that a forced refresh is not needed. Consequently, when RFSH goes low, the DRAM controller continues with normal operation.

On the 5036A, enter the following keystrokes:

```

FETCH ADDR

8000

C3

STORE/INCR

00

STORE/INCR

80

STORE/INCR

FETCH ADDR

8000

RUN

```

This short program gets address 8000 in DRAM, stores address 8000 as the jump address, and jumps back to itself. In other words, it continually loops back to address 8000. Since this address is in DRAM, it should cause a forced refresh, because the 8409 will never detect the microprocessor trying to access something else. The 8409 never finds time to slip in a hidden refresh.

Press the RUN key on the HP 1631.

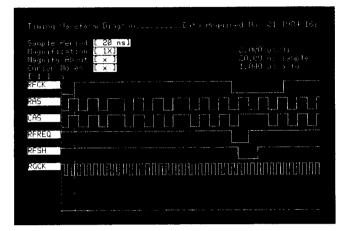

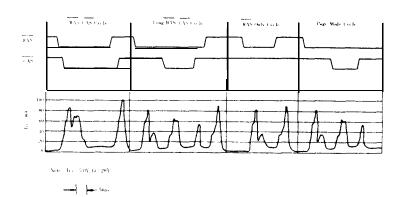

With the trace specification that we have set, we should capture one of the two sequences listed above. The first case (forced refresh) is shown in figure 20.

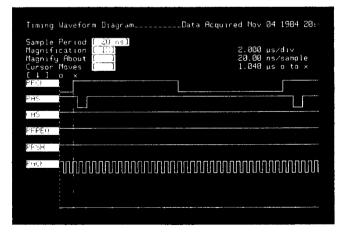

#### Figure 20

Press the RESET key on the HP 5036A. This puts the 5036A back into the keyboard monitor routine. Since it is monitoring only keyboard presses and not accessing DRAM, hidden refreshes should occur all the time. Press the RUN key on the HP 1631.

The second case, that of a hidden refresh is shown in figure 21.

#### Figure 21

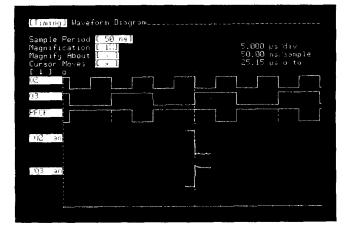

Notice that the tracepoint in both diagrams and on your analyzer is at the left hand portion of the screen. It is represented by the heavy vertical dashed line. Now suppose we want to see more of what occurred before the actual tracepoint (negative time). Press the TRACE key and set the tracepoint to [Center]. Press the RUN on the 1631 to capture new data with the trace point at center. The tracepoint should now appear at the center of the screen with data before and after it.

| Timing Naveform Diagr massac                                                               |                                                    |

|--------------------------------------------------------------------------------------------|----------------------------------------------------|

| Sample Pariod [0 ns]<br>Magnification []<br>Magnify About []<br>Curson Moves []<br>[4] o × | 2.000 us∕div<br>20.00 ns/sample<br>1.640 us o to x |

|                                                                                            |                                                    |

|                                                                                            |                                                    |

|                                                                                            |                                                    |

|                                                                                            |                                                    |

#### Figure 22

If you set the tracepoint at [End], the tracepoint will be at the right side of the screen with all of the events before the tracepoinr displayed to the left.

Change the trace point back to [Start].

As mentioned earlier, it is sometimes helpful to display the timing information in a list form in addition to the waveform display. If you press the LIST key, which is one of the six along the top of the keyboard, a list representation appears of what is on-screen. Notice that you can shift from the trace specification, to format specification, to waveform diagram, to list representation by pressing one of the six: keys along the top of the keyboard. These keys represent the major functional areas of the analyzer, although some are not appropriate for certain operations.

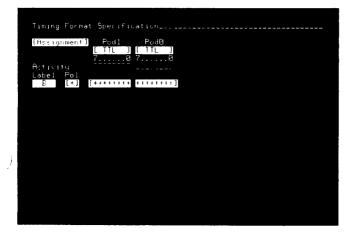

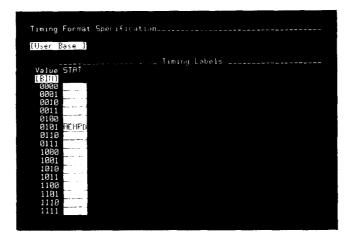

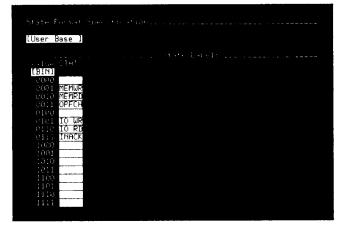

In the list mode, all of the data is listed as a 0 or 1. This is appropriate, but suppose we would like some labels, other than 1 and 0, that are more descriptive of what those two numbers represent. Let's use an example. In the case of RFREQ (REFRESH REQUEST), when the signal is low, a forced refresh is requested. When the line is high, a forced refresh is not requested or the system is looking for a hidden refresh. So instead of 0 and 1 in the list, it would be clearer to display them as RFREQ, and IDLE, respectively. By the same reasoning, we could label the 0 and 1 states of RFSH as FRFSH (for forced refresh) and IDLE, respectively. Press the FORMAT key and move the cursor to the [Assignment] field. Press the NEXT[] or PREV[] key to enter the [User Base] menu. Notice that for each of the signals previously defined in the format menu, there are two highlighted blocks representing 0000 and 0001. The number of blocks is determined by how many bits were set in the assignment menu. In each case, we defined only one bit for each signal. That gives two

possible states, (on or off) for each. Consequently, there are two highlighted blocks shown for each of the signals. Even though there are two states for each signal, these states can be labelled anything you like. This allows you to assign labels that are more meaningful to the particular signal than just ON and OFF, or 1 and 0.

Position the cursor and enter the labels as shown from the keyboard.

| Timing               | Forma  | t Spec | ificat | 10n   |      |  |  |

|----------------------|--------|--------|--------|-------|------|--|--|

| [User_B              | lase l |        |        |       |      |  |  |

| Value                | PECK   | PAS    |        |       |      |  |  |

| EB1(1)<br>8688       |        |        |        | REPEO | FREF |  |  |

| 0001<br>0010         |        |        |        | IDLE  | IDLE |  |  |

| 8011<br>8108         |        |        |        |       |      |  |  |

| 0101<br>0110         |        |        |        |       |      |  |  |

| 0111<br>1000         |        |        |        |       |      |  |  |

| 1001<br>1010<br>1011 |        |        |        |       |      |  |  |

| 1100<br>1100<br>1101 |        |        |        |       |      |  |  |

| 1110                 |        |        |        |       |      |  |  |

| 1111                 |        |        |        |       |      |  |  |

#### Figure 23

Press the LIST key and move the cursor to the Base field below RFREQ. Using the NEXT[] or PREV[] key, cycle through the choices until (USR] is displayed. This is the user-defined base. Do the same for RFSH and look at the list. All of the 0s and 1s have been replaced with the names you entered into the user base. Notice that the measurement does not have to be re-run. This feature makes a list much easier to read and eliminates the need for you to recall exactly what each state means for each labeled signal. User base accepts signals with up to 4-bit lengths, as assigned in the format [Assignment] menu, for a possible list of 16 states for each signal. Each of these 16 states can be labeled with a descriptor, as was done with the two states of RFREQ and RFSH.

# Using The Timing Analyzer Within The HP 1631A/D (continued)

There are several other advantages of the list format. Suppose you want to look for a unique pattern that represents a forced refresh in your data. One way to find it would be to look at the timing diagram and check the state of each line until you found what you were looking for, assuming that it happened within your acquisition. An easier way is provided in the list mode. During forced refresh, we know that RFCK, RFREQ, and RFSH are all low. This indicates that the refresh clock (RFCK) has gone low, that a forced refresh request (RFREQ) has been issued to put the microprocessor in a HOLD state, and that the refresh has been acknowledged (RFSH) by the processor, saying that it is in HOLD state while the 8409 refreshes the RAMs. Press the LIST key and position the cursor in the [Mark] field. To the left of the

| Timing           | Listing         |              |       |                  | Acquired      | Hov 01        | 1984-16:'   |

|------------------|-----------------|--------------|-------|------------------|---------------|---------------|-------------|

| Label:<br>Ba≤e : | RF()<br>[B](1]] | PHS<br>[BIH] | (BIN] | PEREG<br>[ USR ] | PFIH<br>[USR] | PGC)<br>[BIN] |             |

| (Marti)          |                 |              | 8     | [PFREQ]          | (F REF)       | X             | Externe     |

| -0183            | 0               | U.           |       | REREU            | 10LE          |               | -3.660 pr   |

| -0182            | k1              |              |       | PEPED            | IDLE          |               | 3.640 .     |

| -0101            |                 |              |       | 토토 만든 것          | 10LE          |               | -3.620 µ    |

| -0180            |                 |              |       | PEPEQ            | IDLE          | ú             | -3.600 u    |

| -8179            | Û               |              |       | PEPEO            | IDLE          |               | 3.580 u     |

| -8178            |                 |              |       | PEPEO            | IDLE          |               | -3.560 p    |

| -8177            |                 |              |       | REPEU            | IDLE          | Ĩ             | -3,540 b    |

| -0176+           |                 |              |       | PEPEO            | F FEF         |               | -3.520 p    |

| -0175*           |                 |              |       | PEFEO            | F PEF         |               | -3.700 µ    |

| -8174*           |                 |              |       | REPEU            | F PEF         |               | -0.480 p    |

| -0173+           |                 |              |       | PEPEL            | E REF         |               | -3.460 p    |

| -0172*           |                 |              |       | PEREN            | 고 3억 귀        |               | -1,440 p    |

| -0171+           | Ð               |              |       | () 글 귀 위         | F F E F       |               | - 3. 430 pr |

| -0170+           |                 |              |       | REPER            | E FEF         |               | -3.400 p    |

| -0169*           |                 |              |       | PERED            | 귀경의 귀         |               | -3.380 p    |

| -0168*           |                 |              |       | REPEN            | F FEF         | 1             | - 3. 16th u |

|                  |                 |              |       |                  |               |               |             |

#### Figure 24

[Mark] and under each signal name, there is a field that has an X for Don't Care in it, or in the case of the two signals we labeled, RFSH and RFREQ, there is a bracketed field with several Xs. These allow us to tell the analyzer to search its data for a unique pattern. Move the cursor to the field under RFCK and enter a 1 from the keyboard. Now move the cursor to the same fields under RFREQ and RFSH and using the NEX[] key, cycle through until the analyzer displays RFREQ and FREF in the fields. All occurrences of that pattern are now marked with an "\*" next to the memory location at the left of the screen. We could scroll through the whole memory with the ROLL keys to find all of those occurrences, but it is unnecessary. Move the cursor back to the [Mark] field and press NEXT[]. The field displays [Show], and the list displays only those occurrences of the unique pattern you requested.\* Using the ROLL keys, scroll down in the list. Press the WAVEFORM key and notice that the point you were in in the list is marked on the waveform with the X marker. You have found the occurrences of a forced refresh on the waveform using the list format.

\*If the analyzer doesn't display anything, it means that it didn't capture a forced refresh cycle. You may want to press the RUN key until one is captured.

**Conclusion:** with very little pain, you have used the timing analyzer to capture and display some of the more important control signals on the DRAM board. The waveform display allowed you to see the signals as they related to each other in time without unnecessary parametric information. You also saw the information in a list format and learned to put more meaningful information into it than 0s and 1s. When you are concerned about time sequences of hardware events, the timing analyzer gives you a lot of information with little visual clutter. It also gives you negative time, which allows you to look at data before the specified tracepoint. This was exemplified when you set the tracepoint to be displayed in the center of the screen, rather than at the start.

This measurement was intended to give anyone who has not used a timing analyzer some familiarity with one and to build confidence that there really isn't any magic in logic analyzers. When compared to an oscilloscope, a timing analyzer is an extension that allows you to deal with a different set of problems. The next few measurements cover some actual design concerns in DRAM design and show how the feature set of the HP 1631A/D is suited to the hardware designer's needs.

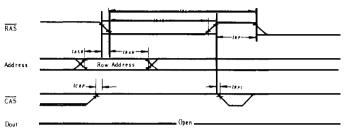

### Measurement 6: Using The Timing Analyzer And Post-processing To Determine Maximum Forced Refresh Time.

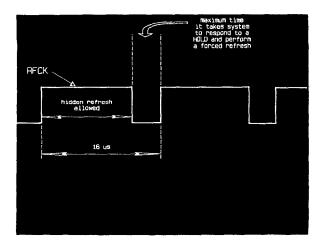

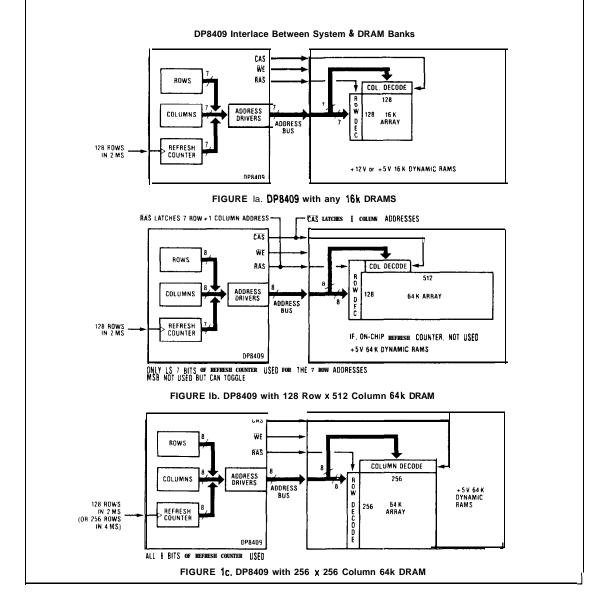

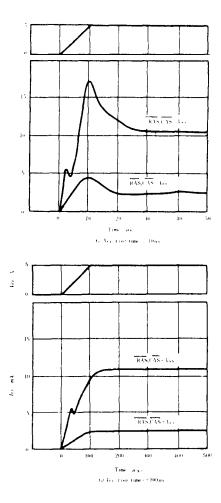

Description: The 64k DRAMs on the board have a maximum refresh time of 2 ms. The RAMs have 128 rows x 512 columns, internally. All memory cells in a row can be refreshed by accessing that row with a RAS pulse. So, to refresh the whole KAM, all 128 rows must be refreshed within the 2 ms cycle time. The amount of time spent on each row is then 2 ms/128 rows = 15.6  $\mu$ s, or 16  $\mu$ s to round off. This time is the period of the clock given to the 8409 DRAM controller at pin 1 as the refresh clock (RFCK). Using either hidden or forced refresh, the row the controller is accessing must be refreshed within that 16  $\mu$  s. Hidden refresh is allowed on the positive portion of RFCK. When RFCK goes low and if a hidden refresh has not occurred, the 8409 initiates a forced refresh. The problem with forced refresh is that the 8409 must request that the system processor suspend all exterior operations while it refreshes the RAMs. The processor is then essentially idle during this time. How long is this time? According to the 8409 data sheet, a forced refresh takes approximately four cycles of the system clock, or in the case of the 5036A with a 2 MHz clock: 500 ns x 4 = 2  $\mu$ s. Since, in worst case, this 2  $\mu$ s forced refresh could happen every cycle if a hidden refresh can't be performed, the processor could be idle as much as 2  $\mu$ s/16  $\mu$ s = 12.5% of the time. In many cases, this might clearly be unacceptable. What to do!

Luckily, there is nothing to prevent us from making the clock asymmetrical to allow more time for a hidden refresh to occur. Remember from our discussion in Appendix A that the 8409 looks at the chip select line and slips a hidden refresh in whenever the processor is accessing something besides its DRAMs. By lengthing the time that RFCK is high, we are creating a greater probability that the processor will access something other than RAM, and a hidden refresh can be performed. But we need to know the time that it really takes for the processor to react to a forced refresh request, since that impacts how long RFCK can remain high.

#### Figure 25

We will use the post processing capability of the timing analyzer to determine the maximum time it takes for the processor to respond to a HOLD request from the 8409, added to the time it takes the 8409 to perform a refresh.

**Set up:** the DRAM board has a switch that allows a symmetrical or asymmetrical clock. Since we want a symmetrical clock, make certain that S1 is in the open position.

Use the same physical connections to the system as was used in measurement 5.

Use the same format specification as in measurement 5.

What point should we set the analyzer to trace on? First, let's determine the start of the cycle. Clearly, the next cycle starts when RFCK goes high. Set the trace specification as in figure 26.

# Using The Timing Analyzer Within The HP 1631A/D (continued)

| Timing [                               | Tr <u>ace</u> Sp | Decific        | ation]    |                      |         |                 | <br> |

|----------------------------------------|------------------|----------------|-----------|----------------------|---------|-----------------|------|

| [ <u>Continu</u> ]<br>[ <u>5</u> ing]( |                  |                |           |                      |         |                 | ÷    |

| Post Pro-<br>Statistic                 |                  |                |           |                      |         |                 |      |

| Sample Pa                              | erusd (          | 50 <u>ns</u> ] |           | ution T              | 10e: 51 | .20 µs          |      |

| [Start]                                | Fride 2          | 1000 (µs       | a] sifter | - <sup>T</sup> rugge |         |                 |      |

| Label<br>Base                          | FF:)<br>[8[N]    | CBIN1          |           | (BIN)                | EBIN]   | RGEK<br>(BIIII) |      |

| Pattern<br>Hrd Ang                     | 3                | X              | ×         | X                    |         |                 |      |

| Edge                                   | [1]              | [[.]]          | [.]       | [.]                  | ['%]    | []]             |      |

| Velid Pat                              |                  |                | [ 1       | µs]                  |         |                 |      |

|                                        |                  |                |           |                      |         |                 |      |

|                                        |                  |                |           |                      |         |                 |      |

#### Figure 26

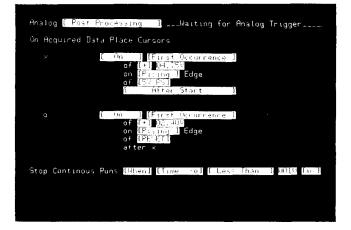

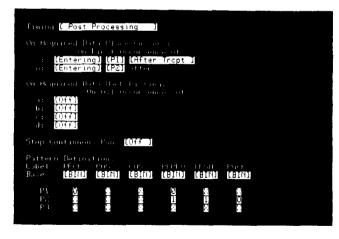

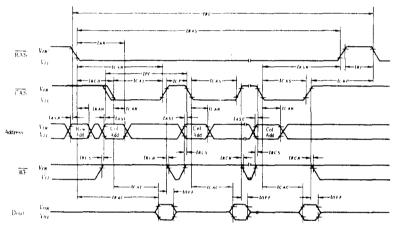

Post-processing in timing allows us to do functions similar to those in analog. We want to set up a postprocessing specification that allows us to measure the actua<sub>i</sub>] refresh time. To get to the post-processing menu, press TRACE and set the post-processing and statistical measurement fields to [On]. Press the TRACE key once more to place the cursor at the top of the screen, and then move the cursor to the right to the field labelled [Trace Specification]. Press the NEXT[] key. Set the postprocessing specification menu to match the one shown.

This post-processing specification tells the analyzer to measure the time between entering a pattern of RFSH going to 0 (the 8409 getting a hold acknowledge from the processor) and entering a pattern of RFSH = 1 (hold acknowledge ended), RFREQ = 1 (hold request ended), and RGCK  $\approx$  0 (the end of the refresh cycle, per the 8409 data sheet). RGCK is the same as the system processor clock, and when it goes to 0 after RFREQ and RFSH have gone to 1, the processor is starting a new cycle after being held off.

Press the FETCH ADDR key on the 5036A and enter the following program into the 5036A.

| FETCH ADDR |

|------------|

| 8000       |

| C3         |

| STORE/INCR |

| 00         |

| STORE/INCR |

| 30         |

| STORE/INCR |

| FETCH ADDR |

| 8000       |

| RUN        |

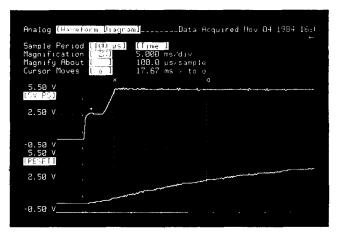

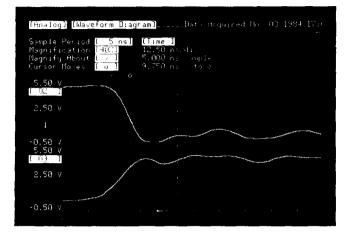

This program, which we used before, forces the DRAM board into forced refreshes, so that we can measure exactly how long they take. Press RUN on the 5036A and on the HP 1631A/D. Let the analyzer run for a minute or so and observe the minimum and maximum numbers on screen. You should get a maximum somewhere around 2.75  $\mu$ s (figure 28). What does that mean?

|       | reation.<br>Fibout ( |     | 5.1660 р.<br>Ласински | -dar []]<br>- mapler - 315 | ime ][Max. | . 8 Min. |

|-------|----------------------|-----|-----------------------|----------------------------|------------|----------|

|       | Boles (              | × ] |                       | to a co                    |            |          |

| RFCK  |                      |     |                       |                            |            |          |

| PAS   | hin                  |     |                       |                            |            |          |

| eas - | nchier               |     |                       |                            |            | 1111     |

| PFREQ |                      |     |                       |                            |            |          |

| PESH  |                      |     |                       |                            |            |          |

| PGCK  |                      |     |                       |                            |            |          |

|       |                      |     |                       |                            |            |          |

It means that the low period of RFCK can be changed to 3  $\mu$ s, allowing an extra 5  $\mu$ s for a hidden refresh to occur. How does this affect our processor overhead? Our old figure indicated that the processor's idle time was 12.5% worst case, based on figures in the 8409 data sheet. But we now have some empirical data to recalculate worst case overhead. If the system's idle time is 2.7  $\mu$ s out of a cycle of 16  $\mu$ s, the processor is actually idle 16.9% of the time. We now know that our processor should not be idle more than 16.9% of the time.

**Conclusion:** using the post-processing features of the HP 1631A/D, we were able to gain empirical data about our system that was more appropriate than average calculations. In many cases, event-driven time interval measurements, like those provided by post-processing in the HP 1631A/D, may allow you to time-characterize parts of your system that would be Impossible to make calculations on.

# Using The Timing Analyzer Within The HP 1631A/D (continued)

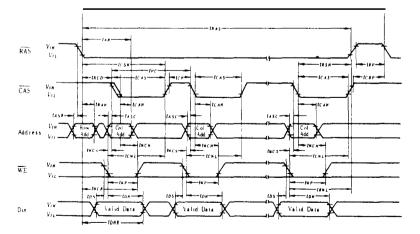

### Measurement 7: Using Timing Post-processing To Determine Actual System Overhead For Refresh

**Description:** in the last measurement, we used timing post-processing to determine the maximum time needed for a forced refresh. This time was in turn used to determine how we could make our system more efficient by increasing the possibility of a hidden refresh. In this measurement, we will again use timing post-processing to determine how much an asymmetrical clock can lower system overhead in actual operation. In measurement 6, we forced the system to perform forced refreshes on every cycle so we could measure how long it took. In normal system operation, at least some hidden refreshes occur. We would like to make measurements to determine the actual idle time of the processor by finding out how many forced refreshes occur in operation. Since there is no way of calculating this, we must rely on a measurement.

We know from previous measurements that the percentage of overhead IS given by the hold time per cycle divided by the time per cycle or hold time/cycle time. To find the total overhead, we must know the ratio of forced refreshes to total number of refreshes. The total system (overhead percentage for forced refreshes should be the product of these two, or:

| total system overhead % | = <u>idle time/cycle</u> x | number of<br>forced refreshes |

|-------------------------|----------------------------|-------------------------------|

|                         | refresh cycle time         | total number of cycles        |

'This may look complex, but it really is quite simple. We are looking for the percentage of a cycle that a forced refresh takes. Secondly, out of a given number of cycles, how many are forced refreshes in normal operation? The product of the two represents the percentage of time the processor spends idle in normal operation. This percentage can just as easily be found for a symmetrical or asymmetrical clock. The percentages can then be compared to see how much of a reduction in system overhead an asymmetrical clock makes.

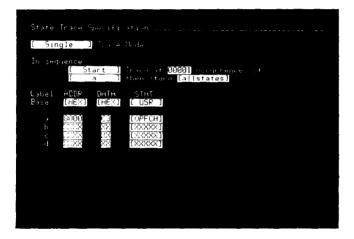

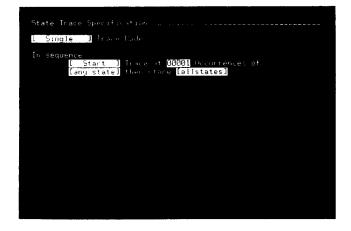

**Setup:** we will use two features of timing postprocessing to help us calculate these percentages. The first was used in measurement 5. The second, which we will use now, is called marking.

All physical connections to the system are the same as in measurement 5.

Switch S l on the DRAM board determines whether the refresh clock RFCK is symmetrical or asymmetrical. Since our first measurement is based on a symmetrical clock, make certain that S l is in the open position.

The format specification is the same as in measurement 6.

Use the same trace specification as measurement 6.

The post-processing menu should reflect the one shown in figure 29.

| antroj [  | Past Pr           | ocessin | g ]                 |         |        |       |   |

|-----------|-------------------|---------|---------------------|---------|--------|-------|---|

| сворни    | en Euro<br>On Eu  |         | tee or .<br>Greence |         |        |       | · |

| . (Er     | ntering]          | {P1]{   | After S             | itart ] |        |       |   |

|           | ed for a<br>Dis   |         | a Janua:<br>Utabupa |         |        |       |   |

|           |                   |         |                     |         |        |       |   |

| 1         |                   |         |                     |         |        |       |   |

|           |                   |         | ff ]                |         |        |       |   |

| 4.003     | ketanata<br>IP}s⊁ | 1917 -  | · ars               | 图积中     | 19 ° H | hta k |   |

|           | [BIN]             | [BIN]   |                     | (BIN]   | [BIN]  | [BIN] |   |

| 81<br>153 |                   | X       | ×.                  | ×       | ×      | 2     |   |

| E.        | 96094             | XIKK    | 110                 | XIIIG   | 1      |       |   |

|           |                   |         |                     |         |        |       |   |

#### Figure 29

In the trace specification menu, the analyzer was set to trace whenever a new refresh cycle started, which is every 16  $\mu$ s. On the timing diagram this number is the "Runs" column. This tells us how many times the trace specification was met and the analyzer captured data. Whenever the trace specification is met, the post processing menu checks the data in memory. In post-processing, we will first set a specification that tells how many forced refreshes occurred. Remember that the first event in a forced refresh is the RFREQ (REFRESH REQUEST) line pulled low. When the post-processor sees this condition in the acquired data, it records it on the timing diagram as a "hit." If we incorporate these two bits of information from the timing diagram into the formula we developed before, we get:

| total system overhead | % = idle time/cycle | number of hits |

|-----------------------|---------------------|----------------|

|                       |                     | number of runs |

Since we know that the refresh cycle time is 16  $\mu$ s, all that is needed to complete the formula is the idle time/cycle. Post-processing provides the mean and standard deviation of marked events, so we will use the mean to calculate the mean cycle time and the standard deviation to calculate our error.

Enter the following program on the 5036A.

FETCH AD DR 0800 00 STORE/INCR 41 STORE/INCR 42 STORE/INCR 41 STORE/INCR 00 STORE/ INCR 80 STORE/INCR FETCH ADDR 4020 RUN FETCH ADDR 8000

Press the RUN keys on the 5036A and the HP 1631A/D. Let the microprocessor lab run for a few minutes, then press the STOP key on the HP 1631A/D. Notice the field beneath the Marks x-o field. It should read [Mean & Dev.]. If it does not, use the NEXT[] key to change it. We now have enough information to complete our equation.

| total system overhead % =      | mean x to 0    | number of hits                        |

|--------------------------------|----------------|---------------------------------------|

|                                | 16 µs          | number of runs                        |

| Timing ble setze ac Drogi en   | Dar e Reguirea | - 10 (17) (19) (17)                   |

| Magnering Hoout [ > ] 34.      |                | he ] [Mean & Dev.<br>H ps Mean S to o |

| PFCF 1<br>PAS PRIMARINA ANNA A |                |                                       |

|                                |                |                                       |

| FFSH                           |                |                                       |

| PGCk Million Andread           |                |                                       |

|                                |                |                                       |

The number you get will probably differ from what is shown, but it should be in the same neighborhood. It represents the mean total percentage of time the processor spent in the hold state for that time.

Now change S 1 on the DRAM board to the closed position and rerun the measurement. To make an accurate comparison, the number of runs for the symmetrical clock and asymmetrical clock should be the same or close to the same.

Did you notice any difference between the first and second runs? This can be a significant improvement in a RAM-based microprocessor system.

Conclusion: efficiency of a system can be difficult to measure from a hardware standpoint. The unique capabilities of the HP 1631A/D allowed us to make a complex measurement in a short time. One comment on post processing should be made here: it takes the HP 1631A/D about 100 ms to post-process the acquired data, and so there is a "dead" time between acquisitions. In the measurement we just made, that means that as many as 6250 refresh cycles may go by between HP 1631A/D acquisitions. That is why the data acquired in post processing should be taken as a statistical measure only. As with all statistical data, the more the HP 1631A/D is allowed to acquire, the higher the confidence level on the results. That also means that if post-processing is used on a repetitive event with a period greater than 100 ms, it is likely that the HP 1631A/D will capture all events.

# Using The Timing Analyzer Within The HP 1631A/D (continued)

### Measurement 8: 'Triggering On Glitches

**Description:** glitches are sometimes the bane of hardware designers, and often the most difficult thing to capture. It seems that if you have a glitch occurring intermittently, you are never able to catch the waveforms that contain the glitches with a timing analyzer. The HP 1630A/D can trigger not only on edges, but on glitches as well. This capability is carried through to the HP 1631A/D.

To create a clock with a 16  $\mu$ s period as is needed by the 8409 DRAM controller, we use a D-latch to divide the 2 MHz system clock down to 1 MHz, which gives a period of 1  $\mu$ s. A 74LS193 4-bit binary up/down counter is then used to divide by 16 to give a period of 16  $\mu$ s. Look at the clock generated trom this circuit (i.e., RFCK), and notice that there is occasionally a glitch in the middle of the pulse. What is causing this glitch?

**Setup:** make the following physical connections to the DRAM board.

| Pod 0 Bit | DRAM Board Connection Point | Signal Name |

|-----------|-----------------------------|-------------|

| <b>0</b>  | U2 pin 6 (74LS193 pin 6)    | Q2          |

| I         | U2 pin 7 (74LS193 pin 7)    | Q3          |

| 2         | U9 pm I (8409 pin 1)        | RFCK        |

Make certain that S1 on the DKAM board is in the closed position.